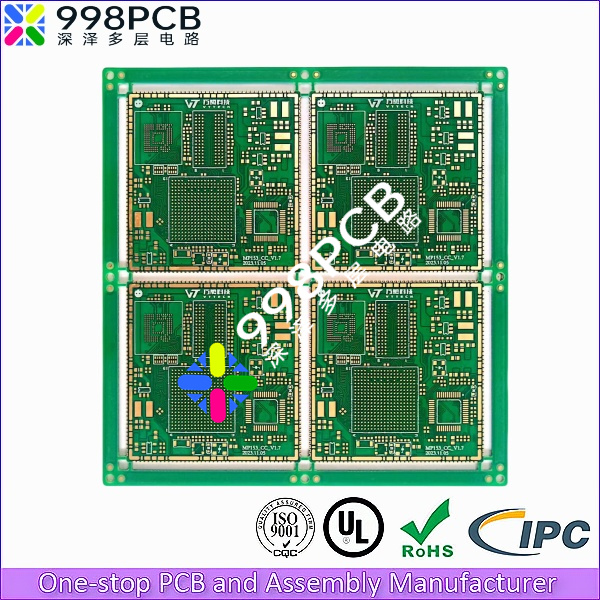

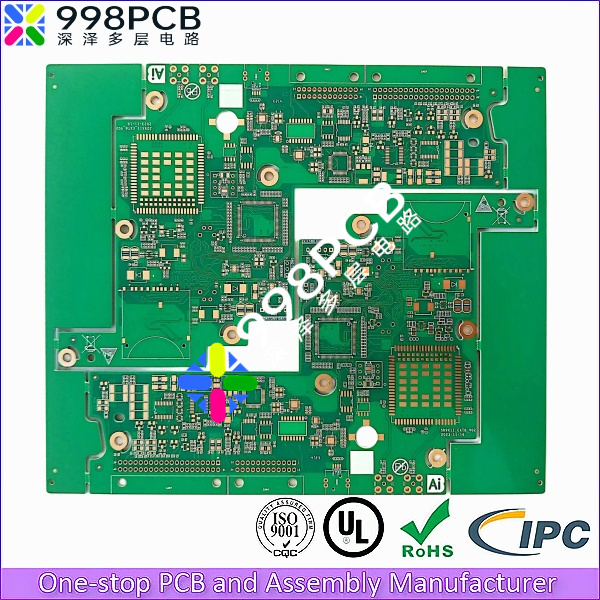

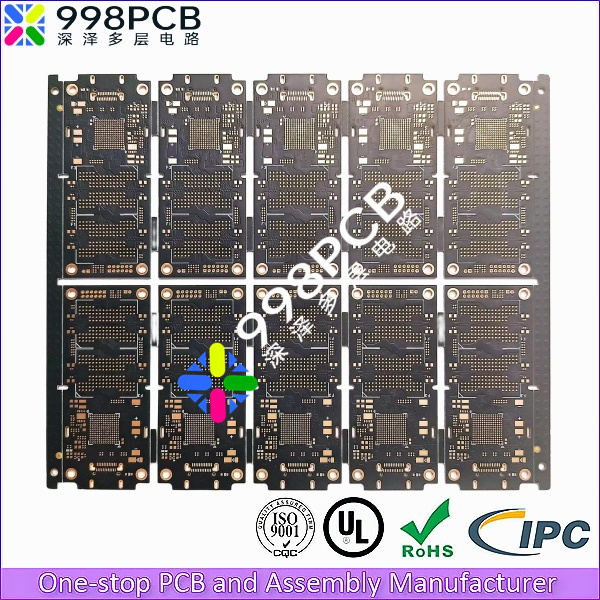

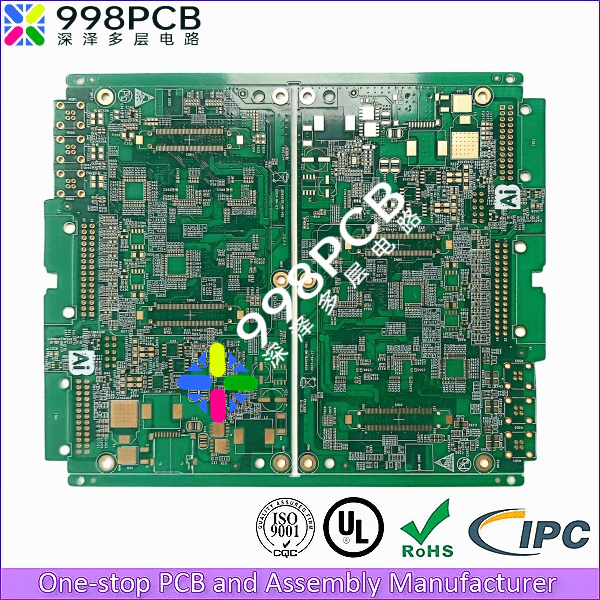

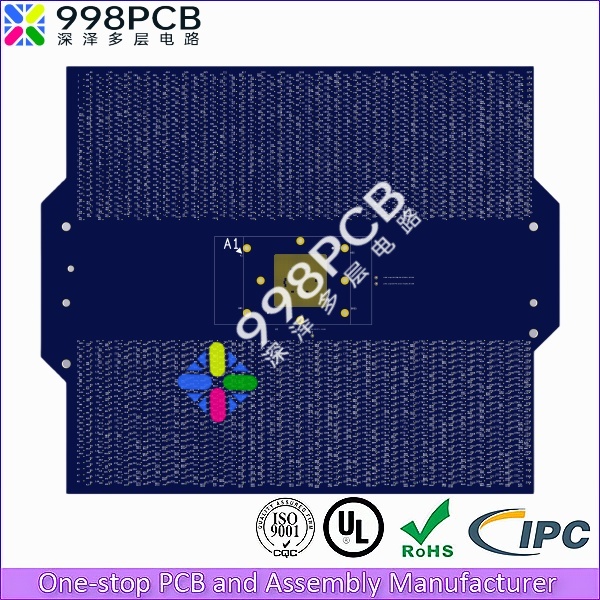

18层芯片测试PCB

18层芯片测试PCB

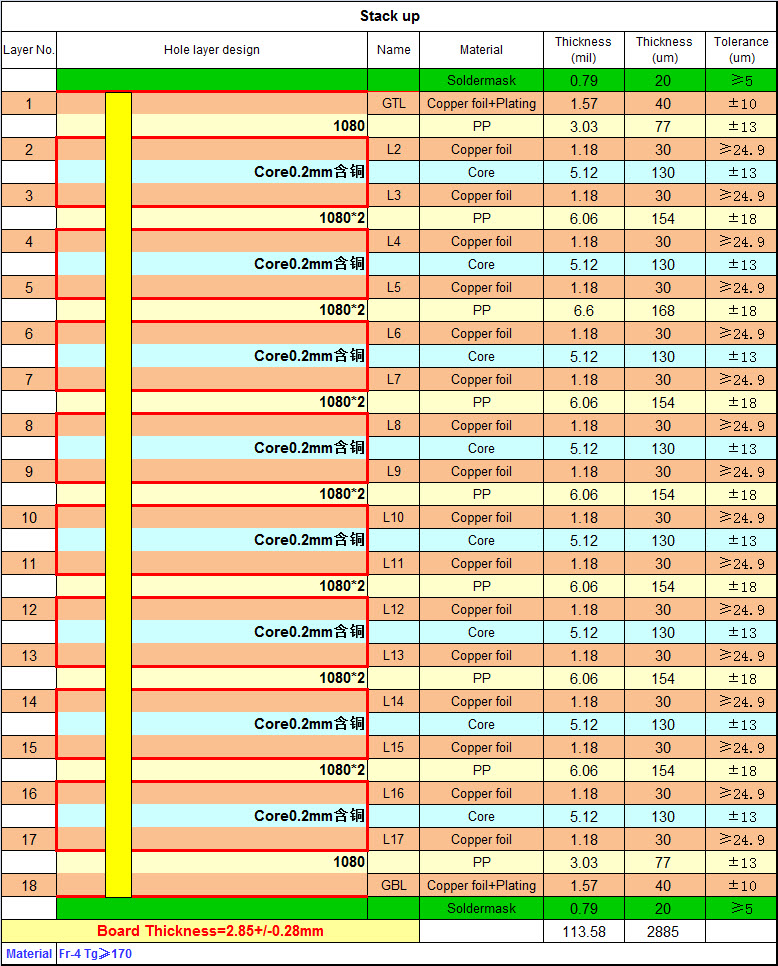

层数: 18L

板材: FR4 S1000-2M

板厚: 2.85mm

拼板尺寸:432*356.5mm/1

外层铜厚: 1OZ

内层铜厚: 1OZ

最小孔径: 0.15mm

线宽线距: 5/5mil

表面处理: 电金 5μ”

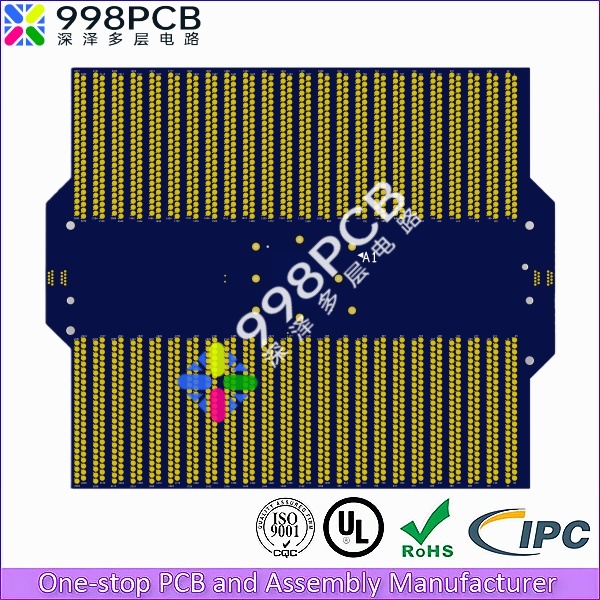

18层芯片测试PCB,BGA点数2973,主要用于芯片功能验证、性能评估、质量控制、可靠性测试等。

满足高端芯片在测试阶段对性能、可靠性与兼容性的严苛要求,我们基于客户提供的技术规格,完成了此款18层芯片测试板的叠层结构与关键工艺设计。本方案精准实现了2.85mm板厚控制、0.15mm微孔及电硬金表面处理,确保测试板能够胜任从功能验证到可靠性评估的全流程测试任务。

芯片测试PCB:半导体产业的关键使能技术

引言

在全球数字化浪潮的推动下,半导体芯片已成为现代信息社会的核心基石。从智能手机到数据中心,从自动驾驶汽车到工业物联网,芯片的性能和可靠性直接决定了整个电子系统的品质。然而,在这片微小的硅片真正应用于终端产品之前,必须经过严苛而全面的测试验证。在这一过程中,芯片测试PCB(Printed Circuit Board)扮演着不可或缺的角色——它既是芯片与测试设备之间的物理桥梁,也是确保测试精度与可靠性的关键技术载体。随着芯片集成度的指数级增长和封装技术的不断演进,芯片测试PCB正面临着前所未有的技术挑战与发展机遇。

芯片测试PCB的基本概念与分类

芯片测试PCB是专为半导体器件测试而设计的印刷电路板,其主要功能是为被测芯片(Device Under Test, DUT)提供稳定的电气连接、精确的电源供应、高速信号传输以及可靠的机械支撑。与普通PCB相比,测试PCB对信号完整性、电源完整性、热管理和机械精度有着更为苛刻的要求。

根据测试阶段和应用场景的不同,芯片测试PCB主要可分为以下几类:

负载板(Load Board)是应用最广泛的测试接口板,用于封装后芯片的最终测试(Final Test)。它通过插座或焊接方式连接被测芯片,将芯片引脚映射到测试机台的通道,并提供必要的匹配网络、滤波电路和电源分配系统。高端负载板通常采用20层以上的多层结构,以应对复杂电源分布和信号布线需求。

探针卡(Probe Card)用于晶圆级测试(Wafer Sort),直接对未切割的晶圆上的芯片进行筛选。探针卡PCB需要与精密探针阵列配合,在微米级尺度上实现与芯片焊垫的可靠接触,其平面度、定位精度和信号保真度要求极高。

老化板(Burn-in Board)用于芯片的可靠性筛选,在高温(通常125℃以上)和满负荷条件下加速芯片的早期失效。老化板PCB必须采用特殊耐高温材料,并具备优异的热稳定性和长期可靠性。

特性评估板(Evaluation Board)用于芯片性能评估和应用开发,通常包含丰富的接口电路、测量点和调试功能,帮助客户充分理解芯片特性。

关键设计要素

芯片测试PCB的设计是一项跨学科的复杂工程,需要在电气性能、热学特性和机械结构之间取得精妙平衡。

信号完整性(Signal Integrity, SI)是首要考虑因素。随着现代芯片I/O速度突破112Gbps PAM4甚至更高,传输线效应变得极为显著。设计人员必须精确控制特征阻抗(通常50Ω单端或100Ω差分),通过3D电磁场仿真优化走线几何结构,最小化插入损耗和回波损耗。关键信号线需要采用微带线或带状线结构,避免 stubs、锐角和不必要的过孔。对于多千兆位信号,还需考虑通道间串扰、差分对 skew 以及电源噪声耦合等问题。高端测试板普遍采用低介电损耗材料(如Megtron 6/7、Panasonic MEGTRON等),介电常数(Dk)和损耗因子(Df)在宽频率范围内的稳定性至关重要。

电源完整性(Power Integrity, PI)同样不可忽视。现代SoC芯片在纳秒级时间内可能产生数十安培的电流变化,导致严重的电源轨塌陷和地弹噪声。测试PCB必须设计低阻抗的电源分配网络(PDN),包括充足的去耦电容阵列、低电感电源平面和优化的电流路径。设计师需要通过频域仿真确定目标阻抗,在从低频到GHz范围内部署不同容量的电容(如470μF钽电容、10μF陶瓷电容、100nF高频电容等)。电源平面分割、回流路径连续性和同步开关噪声(SSN)抑制是设计难点。

热管理设计直接影响测试精度和芯片安全。测试过程中芯片功耗可能超过数百瓦,若热量不能有效散发,将导致结温过高、性能漂移甚至永久性损坏。测试PCB通常集成散热铜块、热管和风扇接口,在高功率区域采用厚铜箔(2oz以上)和金属基板增强导热。热仿真软件用于预测温度分布,优化散热结构布局。对于极端情况,还需考虑液冷或TEC半导体制冷方案。

机械精度与可靠性是测试PCB的物理基础。板厚公差需控制在±5%以内,平面度要求优于0.5mm/100mm,以避免测试插座接触不良。材料选择需权衡CTE(热膨胀系数)匹配性,特别是陶瓷基板和有机基板混合设计时。反复插拔和高温循环要求PCB表面涂层具有优异耐磨性和抗氧化性,硬金(Hard Gold)或化学镀镍浸金(ENIG)是常见选择。

制造工艺与挑战

芯片测试PCB的制造代表了当前PCB工艺的最高水平,其技术难度远超普通商用板。

高层数与高密度互连(HDI)是基本特征。高端负载板普遍采用20-40层结构,线宽/线距达到50μm/50μm甚至更小。激光钻孔技术用于制作微盲孔和埋孔,孔径可小至75μm。任意层互连(Any-layer HDI)技术使每层都能实现精细布线,极大提升设计灵活性。但层数增加带来层间对准、压合均匀性和热应力控制等挑战,需要高精度的数控钻孔和层压设备。

材料选择与处理极为关键。高速材料如Panasonic MEGTRON6、Isola I-Tera MT40具有优异电气性能,但加工性差、成本高。这些材料钻孔时易产生树脂钻污,需要特殊的去钻污工艺。铜箔粗糙度影响高频损耗,超低粗糙度(VLP、HVLP)铜箔的应用日益普及。对于老化板,聚酰亚胺(PI)或BT树脂等耐高温材料是必选,其玻璃化转变温度(Tg)需超过200℃。

表面处理技术直接影响测试接触可靠性。硬金镀层厚度需精确控制在0.5-1.5μm,硬度大于130Hv,以确保探针或插座万次以上的插拔寿命。化学镀镍钯金(ENEPIG)因其优异的可焊性和打线性能,在细间距应用中备受青睐。局部电镀技术可在同一PCB上实现不同区域的不同表面处理,优化成本与性能。

制造过程控制要求近乎苛刻。关键线宽的公差需控制在±10%以内,阻抗测试 coupon 必须与产品板同工艺制作。自动光学检测(AOI)和X射线检测用于发现微短/微开路,但某些潜在缺陷仍需通过飞针测试或专用夹具测试才能发现。板弯板翘控制贯穿整个制程,从层压参数优化到成品烘烤平整都需严格管理。

当前主要挑战包括:1)信号频率突破100GHz时传统PCB材料与工艺面临极限;2)Chiplet和异构集成要求测试板支持多芯片协同测试;3)成本压力推动测试板向标准化、模块化发展;4)环保法规限制含铅焊料和某些阻燃剂使用。

测试技术与方法

芯片测试PCB的价值最终体现在测试效能上。现代测试策略呈现多样化与智能化趋势。

功能测试验证芯片逻辑功能是否符合设计规范。测试矢量通过测试机台经PCB加载到芯片,输出响应被采集比对。边界扫描(JTAG)和内置自测试(BIST)技术降低了对测试通道的依赖。测试PCB需保证矢量传输的比特错误率低于10⁻¹²,这在112Gbps速率下极具挑战。

参数测试测量芯片的直流和交流电气特性,如工作电流、I/V曲线、上升时间、抖动等。这要求测试PCB具备极高的信号纯净度和测量精度。开尔文连接(Kelvin Connection)用于消除接触电阻影响,实现精确电压测量。低噪声设计包括独立模拟/数字地平面、屏蔽结构和电源滤波。

可靠性测试筛选早期失效芯片。老化测试在高温和动态工作下进行24-168小时,PCB的耐高温和长期可靠性至关重要。温度循环测试验证芯片与封装在热应力下的完整性,要求测试板CTE与芯片匹配。静电放电(ESD)保护设计贯穿PCB全层,避免测试过程损伤芯片。

自动化测试设备(ATE)接口标准化推动测试板设计规范化。PXIe、OpenTop等标准接口定义了机械尺寸、引脚排列和电气规范,使同一测试板可适配不同供应商机台,降低总体测试成本。测试板内置的识别芯片(EEPROM)存储板卡参数和校准数据,实现即插即用。

数据分析与智能测试是新兴方向。测试PCB集成传感器监测电压、温度、湿度等参数,数据实时上传至云端分析。机器学习算法用于预测测试良率、优化测试流程和识别潜在缺陷模式。这种”智慧测试板”概念将测试从单纯筛选升级为工艺反馈和质量预测工具。

发展趋势与展望

展望未来,芯片测试PCB技术将沿着几个关键方向演进:

三维集成与嵌入式组件将更多无源元件(电阻、电容、电感)埋入PCB内部,缩短电气路径,提升高频性能。TSV(硅通孔)技术引入PCB,实现垂直方向高密度互连,缓解平面布线拥堵。

异构集成测试要求单块测试板支持逻辑芯片、HBM内存、光引擎等多种Chiplet的协同测试。这驱动测试板向更高密度、更复杂电源管理和更强散热能力发展,同时需要支持芯片间高速互连的测试。

新材料革命正在酝酿。液晶聚合物(LCP)和聚四氟乙烯(PTFE)复合材料在太赫兹频段表现优异,可能突破传统FR-4体系瓶颈。石墨烯增强铜箔和低介电常数树脂的研发持续推进,有望实现更低损耗与更低成本。

绿色制造与循环经济成为行业共识。无铅无卤材料全面普及,PCB回收技术关注贵金属提取和基材再利用。模块化设计理念使测试板部分组件可升级替换,延长使用寿命,减少电子垃圾。

人工智能辅助设计将变革传统流程。AI算法可自动优化PDN设计、预测SI/PI问题并生成布线方案,将数月的设计周期缩短至数周。数字孪生技术实现虚拟调试,大幅减少昂贵硬件迭代次数。

结语

芯片测试PCB虽隐身于半导体产业链的后端,却是连接芯片设计与终端应用的咽喉要道。它不仅是技术密集型的精密制造产品,更是保障芯片质量、提升良率、控制成本的战略性工具。在中国半导体产业奋力追赶的当下,突破高端测试PCB的设计与制造瓶颈,建立自主可控的供应链体系,对提升整体产业竞争力具有深远意义。随着后摩尔时代 chiplet、3D集成等新架构的普及,测试PCB技术将持续演进,在更微小、更快速、更复杂的芯片世界中扮演越发关键的角色。这一领域的每一点技术进步,都在为数字经济的坚实底座添砖加瓦,其价值超越电路板本身,延伸至整个信息社会的可靠运行。