HDI打样交期长的原因?

HDI打样周期长

在电子科技飞速发展的时代,高密度互连(HDI)线路板凭借其能够制造紧凑、高集成电路板的优势,广泛应用于航空航天、汽车、消费电子、军事等众多领域。然而,在HDI线路板从设计到成品的过程中,打样阶段却常常面临交期过长的难题。这一问题不仅影响企业产品的研发进度,还可能延误市场投放时机,削弱企业的市场竞争力。深入探究其背后的原因,有助于我们找到优化和改进的方向,接下来将从设计、制造、材料、品质控制四个维度展开详细分析。

一、HDI线路板设计复杂

HDI线路板的设计堪称是微观世界的艺术创作,其采用微观层面的设计理念,追求极致的布线密度和复杂结构。在设计过程中,设计师需要全面考量层数、孔位、布线间距、介电常数等多种关键因素。层数的增加意味着线路布局的空间维度更为复杂,每增加一层,都需要重新规划线路走向,确保各层之间信号传输的稳定性和准确性;孔位的精确设置关乎元器件的安装与连接,稍有偏差就可能导致后续组装出现问题;布线间距在微米级别,极小的误差都可能引发信号干扰,因此必须精确把控;介电常数则直接影响信号的传输速度和质量,设计师需要根据不同的应用场景和性能要求,选择合适的介电常数材料。

为了实现如此复杂的设计,设计师必须依赖专业的EDA(电子设计自动化)工具。这些工具虽然功能强大,但操作复杂,需要设计师具备深厚的专业知识和丰富的实践经验。在设计过程中,从最初的原理图绘制到PCB版图设计,每一个环节都需要反复推敲和验证。即使借助先进的设计工具,一次设计就能完美无缺几乎是不可能的,往往需要经过多次修改和优化,才能达到理想的设计效果。例如,在航空航天领域使用的HDI线路板,对信号传输的稳定性和可靠性要求极高,设计团队可能需要花费数周甚至数月的时间,不断调整设计方案,进行模拟测试和验证,以确保设计满足严苛的性能指标。这种复杂且反复的设计过程,使得设计阶段成为HDI线路板打样周期漫长的首要因素之一。

二、HDI线路板制造难点

HDI线路板的制造过程宛如一场精密的工业交响乐,涉及多个复杂且相互关联的步骤。从开料开始,经过内层图形、内层蚀刻、内层AOI(自动光学检测)、棕化、压合等一系列工序,再到钻孔埋孔、埋孔沉铜、埋孔电镀等关键环节,随后是图形转移、蚀刻、AOI、棕化、压合等重复但不可或缺的操作,还包括激光钻孔、机械钻孔、沉铜、电镀、图形转移、蚀刻、AOI等精细加工,最后经过阻焊、文字、表面处理、外形加工和测试等工序,才能最终完成一块HDI线路板的制造。

每一个工序都需要精确的控制和调整,任何一个环节出现微小的失误,都可能导致整个电路板无法满足设计要求。以钻孔工序为例,HDI线路板通常采用微米级别的加工工艺,对钻孔的位置精度、孔径大小都有着极高的要求。钻孔位置偏差可能导致线路连接错误,孔径不合适则会影响元器件的安装和焊接质量。而且,HDI线路板制造对设备精度和操作人员的技能要求也极为苛刻。操作人员不仅需要熟悉每一台设备的性能和操作方法,还需要具备敏锐的观察力和丰富的经验,能够及时发现并解决生产过程中出现的问题。一旦在制造过程中出现错误,不仅需要花费时间进行修正,还可能需要对之前的部分工序进行返工,这无疑大大延长了打样时间。例如,在进行埋孔电镀时,如果电镀参数设置不当,导致孔内电镀不均匀,就需要重新进行电镀,甚至可能需要对之前的沉铜等工序进行复查和修正,整个过程会耗费大量的时间和成本。

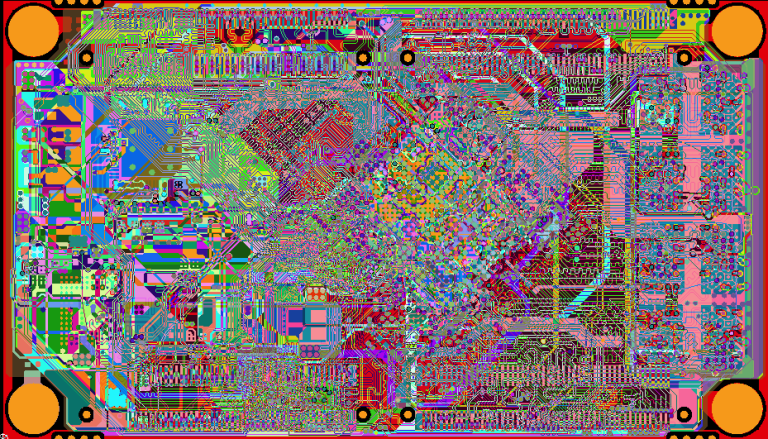

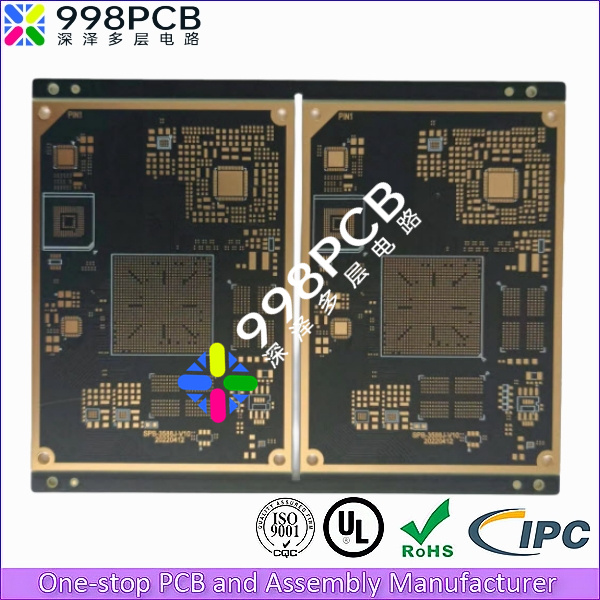

hdi加急打样

层数:10层1阶(1+8+1)

板材: FR4 Tg170

板厚: 1.6mm

拼板尺寸:121.6*95mm/2

外层铜厚: 1OZ

内层铜厚: HOZ

最小通孔: 0.20mm

最小盲孔: 0.10mm

最小BGA: 0.25mm

线宽线距: 3/3mil

表面处理: 沉金1-2μ”

盲孔工艺:填孔电镀

10层1阶hdi加急样品pcb,rk3588核心板,用于工控板。

三、HDI线路板材料要求高

HDI线路板对材料的要求近乎苛刻,为了保证其高性能和可靠性,需要使用高精度的材料。高纯度的铜箔是HDI线路板的关键材料之一,铜箔的纯度直接影响线路的导电性能和信号传输质量。高纯度铜箔的生产过程复杂,需要经过多道提纯工序,其生产周期较长,并且供应相对有限。同时,高介电常数的介质层材料也是HDI线路板不可或缺的组成部分,它能够有效控制信号的传输延迟和损耗,但这类材料的研发和生产难度较大,市场供应不稳定。

由于HDI线路板的特殊结构,还需要使用一些特殊的基板材料,如薄铜箔、薄介电层等。这些特殊材料不仅价格昂贵,而且供应紧张,其采购周期往往较长。在供应链管理方面,HDI线路板生产企业需要与多个供应商建立合作关系,确保各种材料的及时供应。然而,一旦某个环节出现问题,如供应商的生产延误、运输过程中的意外情况等,都可能导致整个生产计划的推迟。例如,某HDI线路板生产企业因供应商的高纯度铜箔供应延迟,导致生产线停工数天,原本计划的打样时间被迫延长,严重影响了客户的项目进度。这种对高精度和特殊材料的依赖,以及复杂的供应链管理,使得材料环节成为制约HDI线路板打样周期的重要因素。

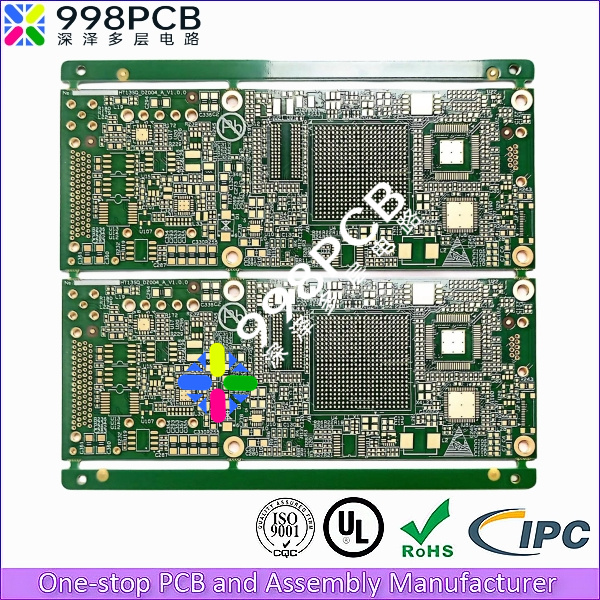

14层2阶hdi打样

层数:14层2阶(2+10+2)

板材: FR4 Tg170

板厚: 1.6mm

拼板尺寸:102*75mm/2

外层铜厚: 1OZ

内层铜厚: 0.5OZ

最小通孔: 0.20mm

最小盲孔: 0.1mm

线宽线距: 2.5/2.5mil

最小BGA: 0.2mml

表面处理: 沉金1-2U”

14层2阶样品HDI,RK3588方案,主要用于高端智能安防、高清图像处理、视频转换、工业控制等产品。

四、HDI线路板品质控制严格

鉴于HDI线路板在电子设备中承担着关键的信号传输和功能实现作用,其品质控制必须做到万无一失。在制造过程中,需要进行多次严格的检测和验证,以确保每一块电路板的质量都符合高标准的要求。从内层AOI检测开始,到后续的多次AOI检测,以及最终的电气性能测试等,每一次检测都是对电路板质量的严格把关。

这些检测过程不仅增加了制造时间,更关键的是,必须保证一次性通过检测。一旦在检测中发现问题,就意味着之前的部分甚至全部工序可能需要重新进行。例如,在最终的电气性能测试中,如果发现电路板存在信号传输异常的问题,就需要追溯到之前的各个制造环节,查找问题根源,可能是线路设计问题、制造工艺问题,也可能是材料质量问题。找到问题后,需要对相关工序进行修正或返工,这无疑会大幅增加时间成本。而且,随着电子设备对HDI线路板性能要求的不断提高,品质控制的标准也在日益严格,检测的项目和精度要求不断增加,进一步延长了打样周期。

综上所述,HDI打样交期长是由设计复杂、制造难点多、材料要求高以及品质控制严格等多个因素共同作用的结果。要有效缩短打样时间,需要从设计优化、制造工艺改进、材料供应链管理以及品质控制流程完善等多个方面入手。企业可以加大研发投入,采用先进的设计工具和方法,提高设计效率;引进更先进的生产设备,优化制造工艺,提升生产精度和效率;加强与供应商的合作,建立稳定的材料供应体系;同时,完善品质控制流程,提高检测的准确性和效率,降低因质量问题导致的返工率。只有通过全方位的优化和改进,才能在保证HDI线路板质量的前提下,有效缩短打样周期,提升企业在市场中的竞争力。

深泽多层电路是一家专业的PCB制造商,致力于高阶HDI、多层PCB、HDI打样、PCB打样、PCB快速打样、高频PCB、高速PCB、FPC、软硬结合板、SMT加工以及PCBA代工代料。他们提供一站式PCB及PCBA制造服务,不仅交期快速,而且价格具有竞争力。他们始终为客户提供高性价比和物美价廉的PCB及PCBA产品。

自2006年成立以来,一直致力于提供高阶HDI、多层PCB、HDI打样、PCB打样、PCB快速打样、高频PCB、高速PCB、FPC、软硬结合板、SMT加工以及PCBA代工代料等一站式制造服务。