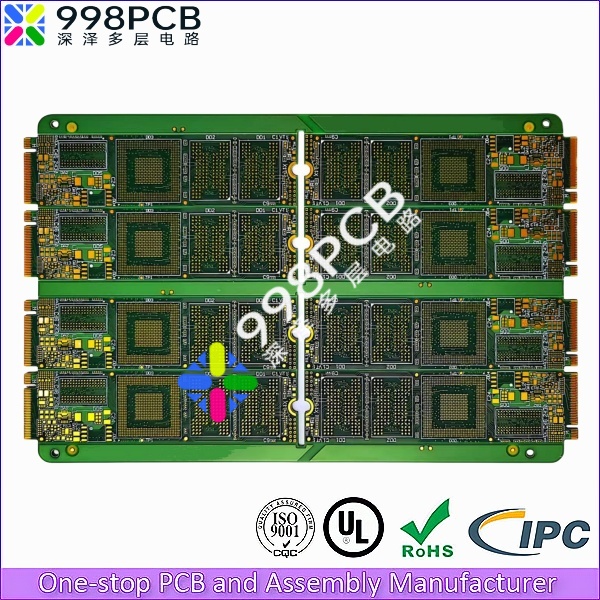

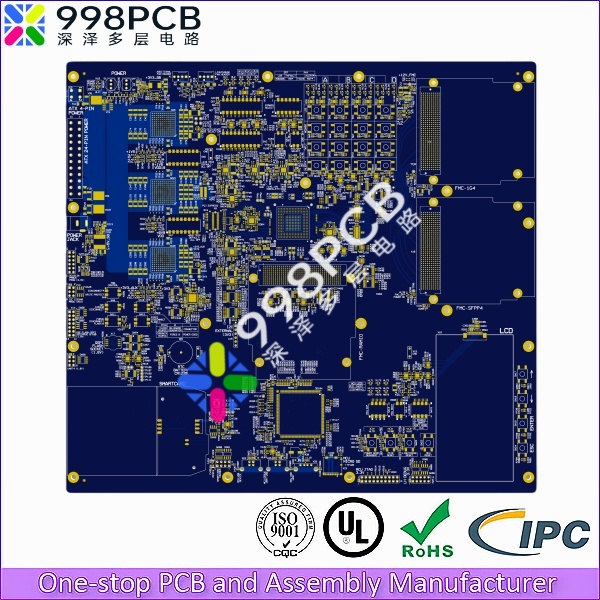

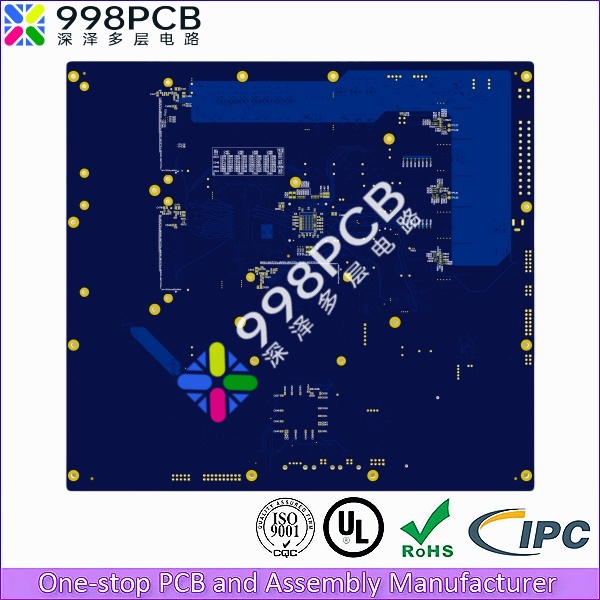

10层高速PCB网络设备

10层高速PCB

层数:10层

板材: Fr4 Tu-883

板厚: 2.0mm

拼板尺寸: 305*280mm/1

外层铜厚: 1OZ

内层铜厚: HOZ

最小通孔: 0.2mm

线宽线距: 3.94/3.93mil

最小BGA: 0.25mm

表面处理: 沉金2U”

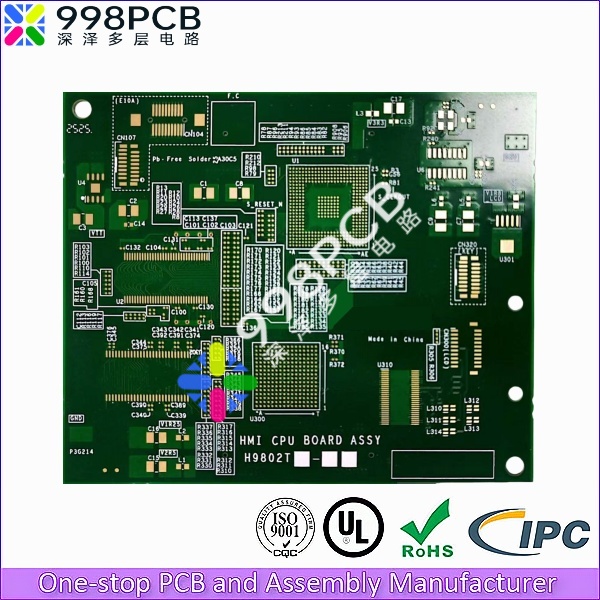

10层高速PCB板,用于工业级网络设备。工业区网络设备是构建工业通信网络的核心组件,主要用于实现设备间的数据交换、远程监控和智能化管理。

鉴于该网络设备对信号完整性具有严苛要求,为彻底解决高速电路中层间信号串扰问题,我们采用了高度定制化的叠层结构设计方案。通过在L3-L4与L7-L8这两组关键信号层之间大幅增加介质厚度——相较于常规设计提升约50%——我们构建了有效的电磁隔离屏障。这一设计有效降低了层间电容耦合,使串扰系数降低至-50dB以下,完全满足万兆级以上网络设备的信号完整性指标。

此项叠层优化不仅解决了并行信号线间的近端串扰(NEXT)与远端串扰(FEXT)问题,同时通过阻抗控制的协同设计,保持了差分信号对的100Ω阻抗匹配精度。在实际测试中,该PCB在25Gbps高速数据传输场景下仍能保持眼图张开度超过0.7UI,误码率优于10-12量级。

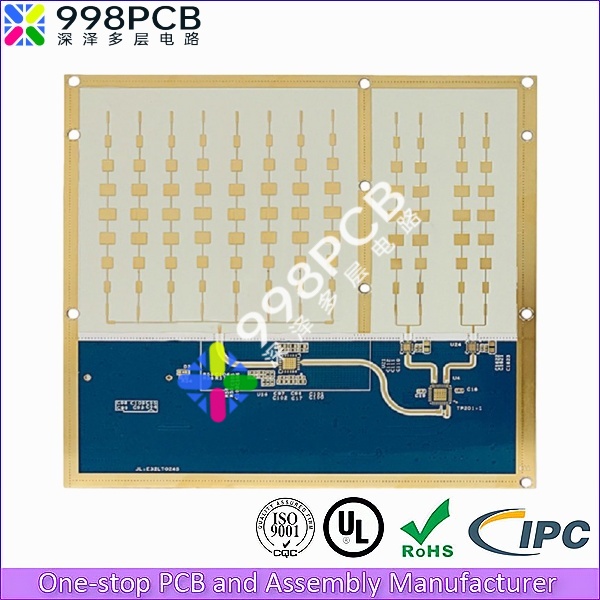

值得一提的是,这种经过特殊加厚的介质结构在提升隔离度的同时,并未影响整体散热性能。我们选用了具有低损耗角正切值(Df≤0.002)的高频材料,确保在提升物理间距的同时,维持优异的高频信号传输特性。该解决方案已通过系统性仿真验证与实测对标,为高端网络设备提供了可靠的PCB平台基础。(下图为我司设计的最终叠层结构)

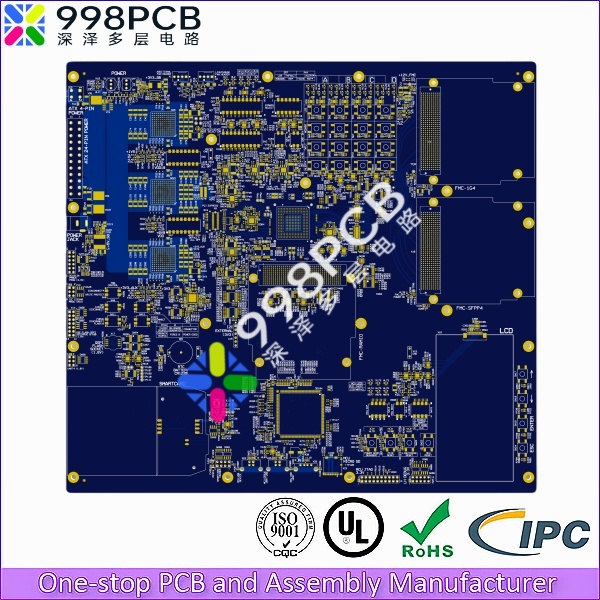

高速网络设备PCB设计如何塑造数字时代

引言:看不见的技术艺术

在数据中心轰鸣的服务器群中,在5G基站寂静的天线内部,一块块多层PCB板正默默地承载着数字文明的洪流。这些看似普通的绿色板卡,实则是网络设备的心脏与神经系统的结合体——它们不仅提供电气连接,更在纳米级的时间尺度上管理着每秒万亿比特的数据流动。本文将从工程实践的角度,深入探讨高速网络设备PCB设计中的关键技术挑战与创新解决方案,揭示这一“沉默基石”背后的科学原理与工程智慧。

一、 网络设备PCB的独特挑战

1.1 速度的永无止境

与消费电子产品不同,网络设备PCB面临着更为严峻的性能考验。从千兆以太网到400G/800G数据中心交换,再到 emerging 1.6T标准,信号速率已从曾经的百兆赫兹跃升至今日的数十吉赫兹。在这种极端频率下,PCB不再仅仅是“导通”的物理载体,而是成为了信号传输通道中不可忽视的电磁环境本身。

1.2 完整性的多维要求

信号完整性(SI)、电源完整性(PI)和电磁兼容性(EMC)构成了高速PCB设计的“三重门”。在实际工程中,这三者相互耦合,形成了复杂的设计约束:

- SI 关注信号波形在传输过程中的畸变程度

- PI 确保芯片供电网络的稳定与纯净

- EMC 管控电磁能量的辐射与耐受能力

任何一方面的妥协都可能导致整机性能的断崖式下跌。

1.3 密度与散热的平衡困境

现代网络设备在追求更高端口密度的同时,还需应对由此产生的热管理挑战。高密度布线会导致通道间距缩小,加剧串扰;而大功率芯片的集中布局则会产生显著的热点,影响材料性能与长期可靠性。

二、 层叠结构:PCB设计的战略蓝图

2.1 层叠设计的基础哲学

层叠结构是PCB设计的战略级决策,它决定了:

- 信号回流路径的完整性

- 阻抗控制的精确度

- 电磁屏蔽的有效性

- 散热通道的合理性

优秀的层叠设计需要在成本、工艺与性能之间找到最佳平衡点。

2.2 针对性介质加厚:工程实践的智慧

正如前文案例中提到的L3-L4和L7-L8层间介质加厚方案,这种针对性强化是解决特定串扰问题的有效手段。其物理原理在于增加层间距离D,根据电容耦合公式 C∝1/D,从而降低层间串扰。在实际设计中,这种加厚不是均匀分布的,而是基于信号流向分析和仿真结果,在关键区域实施的“精准医疗”。

2.3 材料选择的科学

高速PCB介质材料的选择已从传统的FR-4扩展到多种高频特种材料:

- 低损耗材料:如Rogers系列、Taconic系列,其Df值可低至0.002-0.005

- 混合介质结构:在关键信号层使用高性能材料,在其他层保持标准材料

- thermally stable材料:确保在不同温度工况下的稳定性

三、信号完整性防护体系

3.1 串扰的物理机制与治理

串扰源于电磁场的互耦合,包括容性耦合与感性耦合。在实践层面,我们建立了多维防护体系:

物理间距控制

- 邻层走线采用正交布局,减少平行走线长度

- 敏感信号间实施3W-5W规则(线中心间距为线宽的3-5倍)

- 差分对内长度匹配精度控制在意符间隔的1%以内

终端匹配技术

- 使用精确的端接电阻吸收反射能量

- 实施片上端接(ODT)减少离散元件

3.2 阻抗控制的精细化管理

从板材的选购到生产过程中的参数控制,形成完整的阻抗管控链条:

- 设计阶段:利用场求解器进行三维电磁仿真

- 制造阶段:对特征阻抗实施±7%甚至±5%的严格公差

- 测试阶段:采用TDR技术进行实际测量验证

3.3 电源完整性的系统解决方案

为芯片提供“纯净”的电能是现代网络设备PCB的另一大挑战:

- 采用多级去耦网络,覆盖从KHz到GHz的频段

- 优化电源分割与地层设计,提供低阻抗回流路径

- 使用同步开关噪声(SSN)分析与抑制技术

四、从设计到产品的完整链条

4.1 仿真驱动的设计流程

现代高速PCB设计已完全依赖于“仿真优先”的方法论:

- 前期:使用电磁场仿真预测系统性能

- 中期:结合芯片IBIS/AMI模型进行系统级仿真

- 后期:基于实测数据进行模型修正与经验积累

4.2 设计-制造协同

设计与制造的鸿沟是导致产品失败的常见原因。我们建立的协同机制包括:

- 设计阶段充分考虑工艺能力与公差

- 制造阶段提前介入提供工艺建议

- 测试阶段双向反馈形成闭环

4.3 测试验证的科学

从实验室样机到批量生产,建立严谨的测试体系:

- 参数测试:阻抗、插损、回损等基础参数

- 功能测试:误码率、抖动容限等系统指标

- 可靠性测试:温循、振动、老化等耐久性验证

五、未来展望与创新前沿

5.1 新材料与新工艺

- 玻璃基板:为下一代超高频率设备提供解决方案

- 嵌入式元件:将无源器件埋入板内,提升集成度

- 异质集成:将硅光芯片、射频芯片等不同工艺器件集成于同一封装

5.2 设计与验证方法的演进

人工智能与机器学习正在改变传统设计方法:

- 智能布线算法可自动优化信号路径

- 基于大数据的工艺偏差预测与补偿

- 虚拟原型技术缩短开发周期

5.3 可持续发展要求

随着全球对环境保护的重视,PCB行业也面临绿色转型:

- 无卤素基材的推广使用

- 节能减排制造工艺

- 可回收性设计与循环利用

结语

网络设备PCB设计是一门融合了电磁学、材料科学、热力学与制造工艺的复合学科。在这个看不见的战场上,每一微米的介质厚度调整、每一欧姆的阻抗控制、每一度的温度管理,都在静默地塑造着我们的数字世界。正如文中探讨的层叠结构优化案例,工程创新的本质往往不在于惊天动地的突破,而在于对细节的深刻理解与精准把控。随着技术的发展,PCB设计师将继续在信号完整性与系统集成度的双重挑战中寻找最优解,为全球数字化进程奠定坚实的物理基础。