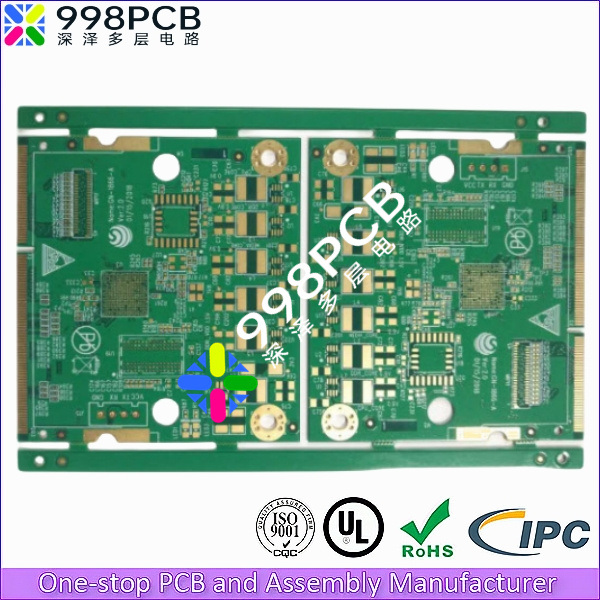

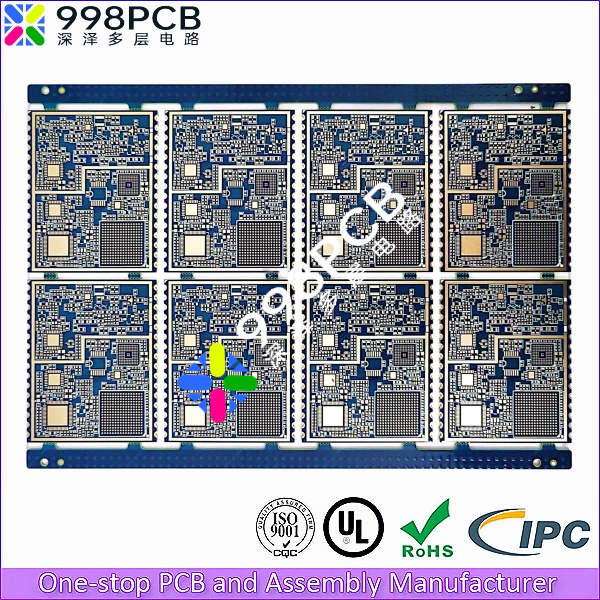

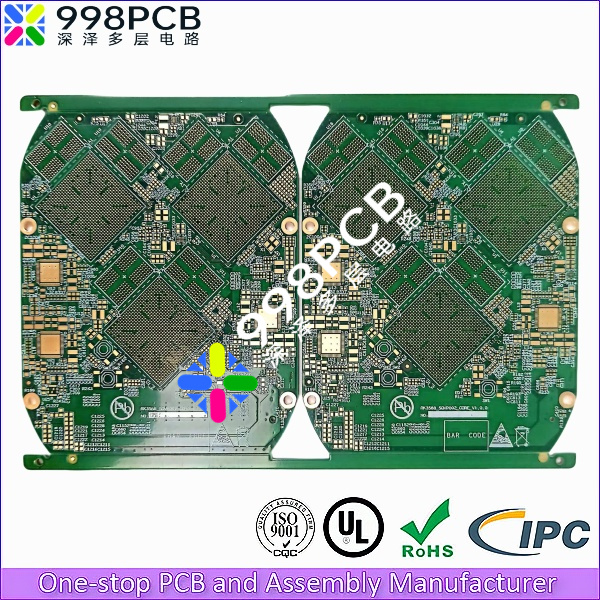

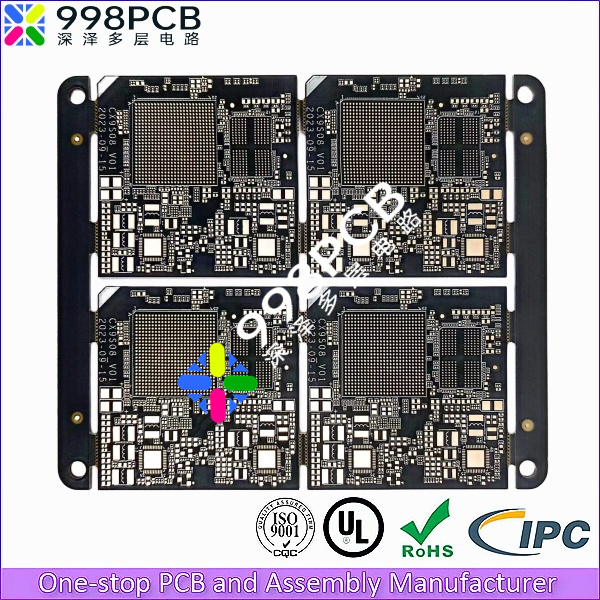

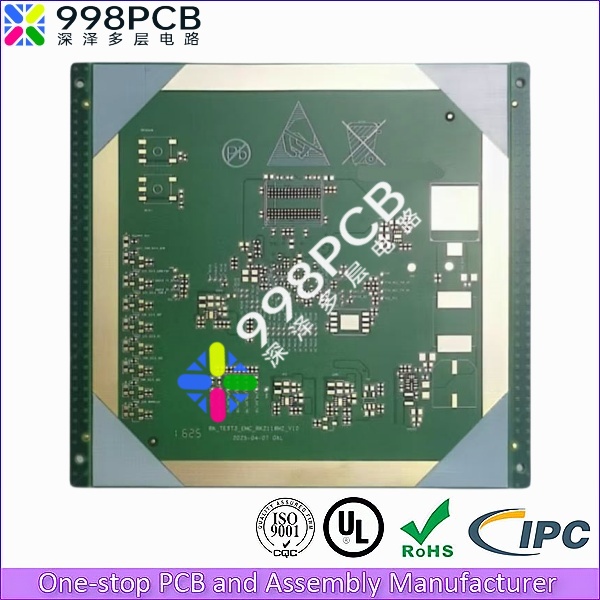

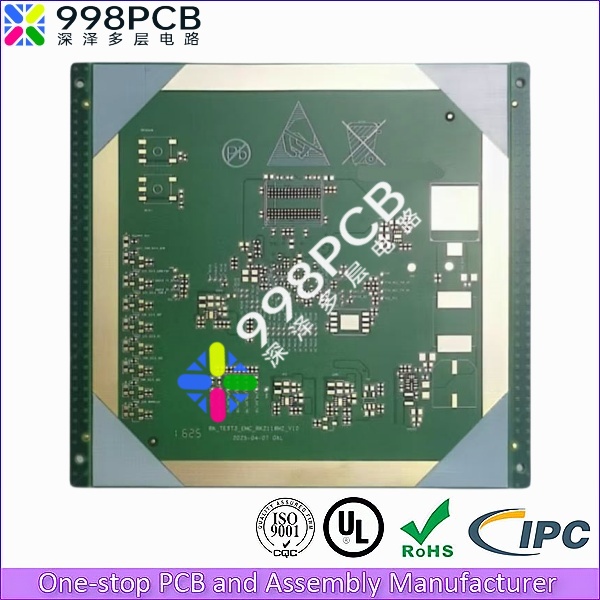

6层1阶IC芯片测试PCB

IC芯片测试PCB

层数:6层1阶(1+4+1)

板材: FR4 Tg170

板厚: 1.6mm

拼板尺寸: 110*100mm/4

外层铜厚: 1OZ

内层铜厚: 1OZ

最小通孔: 0.20mm

线宽线距: 2.5/4mil

最小BGA:0.25mm

表面处理: 沉金1U”

特殊工艺: 填孔电镀+树脂塞孔

6层IC芯片测试PCB,RK2118 处理器,广泛用于半导体制造与封装,电子产品研发与生产,质量检测与故障诊断,为半导体产业乃至整个电子信息领域带来更多的惊喜和变革。

本方案针对客户的高精度IC芯片测试需求,设计开发了板厚1.6mm的6层1阶HDI PCB结构。在充分考量客户提出的内层铜厚1OZ/外层铜厚1OZ的规格要求、±10%的阻抗控制精度以及长期工作稳定性等关键指标后,我司技术团队经过严谨计算与仿真验证,最终确定以下优化压合架构:

- 核心层设计: 采用0.9mm厚FR-4芯板作为中央支撑层,该厚度选择既满足整体板厚要求,又能为多层结构提供必要的机械强度。芯板材料选用Tg170高耐温基材,确保在高温测试环境下的尺寸稳定性。

- 次外层构建: 在芯板两侧对称叠构,各采用2张1080型号PP(Prepreg)固化片进行压合。每张固化片经精确控制达到0.01mm压合厚度,通过此配置实现:

- 精确的介电层厚度控制

- 优化的阻抗匹配性能

- 增强的层间结合力

- 激光钻孔层设计: 外层激光钻孔区域采用特殊结构设计,每侧各配置1张1080PP固化片。该设计具有以下技术优势:

- 将激光钻孔深度严格控制在80-100μm理想范围

- 确保微孔(75-100μm)的加工精度

- 避免孔壁树脂残留问题

- 提高盲孔电镀可靠性

- 工艺保障措施: 配套实施严格的层偏控制(≤50μm)、采用真空压合工艺消除气泡、实施全流程阻抗测试等质量管控手段,确保最终产品达到:

- 阻抗控制精度±8%

- 热应力测试通过3次288℃回流焊

- 高低温循环(-55℃~125℃)测试500次无异常

IC芯片测试板的技术原理与发展趋势

一、引言:测试板在半导体产业中的核心地位

随着半导体工艺节点不断突破5nm、3nm极限,IC测试板作为连接设计验证与量产的关键载体,其重要性日益凸显。现代测试板不仅要满足GHz级高速信号传输,还需应对3D堆叠芯片的复杂测试需求。据统计,2024年全球ATE测试设备市场规模已达78亿美元,其中测试板相关配套占比超过30%。

二、核心技术解析

2.1 基本架构设计

典型测试板采用多层PCB结构(通常16-32层),包含:

- 被测器件(DUT)接口区:采用弹簧针(pogo pin)或MEMS探针阵列

- 信号调理模块:包含阻抗匹配网络和衰减电路

- 电源管理单元:支持±5%精度的多电压域供电

- 边界扫描链:符合IEEE 1149.1/JTAG标准

2.2 关键性能指标

参数类型先进水平测试方法信号完整性眼图高度>80mV@28Gbps矢量网络分析仪时序精度±15ps skew时域反射计热阻系数<0.5℃/W红外热成像

2.3 材料技术突破

最新测试板已开始应用:

- 超低损耗介质:松下MEGTRON6(Df=0.0015)

- 混合堆叠工艺:将有机基板与硅中介层集成

- 纳米银导电胶:烧结温度降至200℃以下

三、典型应用场景

3.1 晶圆级测试

采用微凸点(microbump)技术实现:

- 最小25μm间距探针卡

- 并行测试256个die

- 接触电阻<0.1Ω

3.2 系统级测试(SLT)

创新方案包括:

- 光学互连测试接口

- 基于PXIe的模块化架构

- 机器学习驱动的自适应测试算法

四、前沿发展方向

- 光子集成测试:硅光芯片的耦合损耗检测

- 量子芯片测试:极低温(4K)环境下的微波探针

- 自修复电路:内置BIST功能的智能测试板

五、结论

测试板技术正从”被动连接”向”主动诊断”演进,预计到2028年,集成AI协处理器的测试板将实现测试效率提升300%。建议国内厂商重点突破高频材料、高精度制造等”卡脖子”环节。