一文让你清楚HDI叠孔和错孔的区别

引言

在智能手机、5G通信设备和自动驾驶控制器等高端电子产品的推动下,高密度互连(High Density Interconnect, HDI)技术已成为现代PCB设计的核心战场。叠孔(Stacked Via)与错孔(Staggered Via)作为实现多层互连的两种关键方案,直接决定了电路板的性能极限与制造成本。本文将从结构原理、制造工艺、技术难点、应用场景四大维度,深入解析HDI叠孔和错孔的区别,并揭示其背后的技术博弈逻辑。

一、基础定义与结构特性

1.1 叠孔(Stacked Via):垂直精度的极致追求

定义:叠孔是指多个微孔在垂直方向上完全对齐堆叠的结构,各层孔中心轴线偏差需控制在±15μm以内(IPC-A-600G标准)。这种设计方式旨在通过垂直叠加实现单位面积内最大的互连密度,从而满足高端电子产品对高集成度和高性能的需求。

典型结构:

- 激光盲孔:外层至次外层,孔径通常在50-100μm范围内,利用激光技术实现高精度钻孔。

- 机械埋孔:用于内层间的连接,孔径较大,一般在150-200μm之间,采用机械钻孔方式。

- 电镀填孔:为了确保导电性,叠孔设计需要进行电镀填孔处理,铜厚需≥25μm。

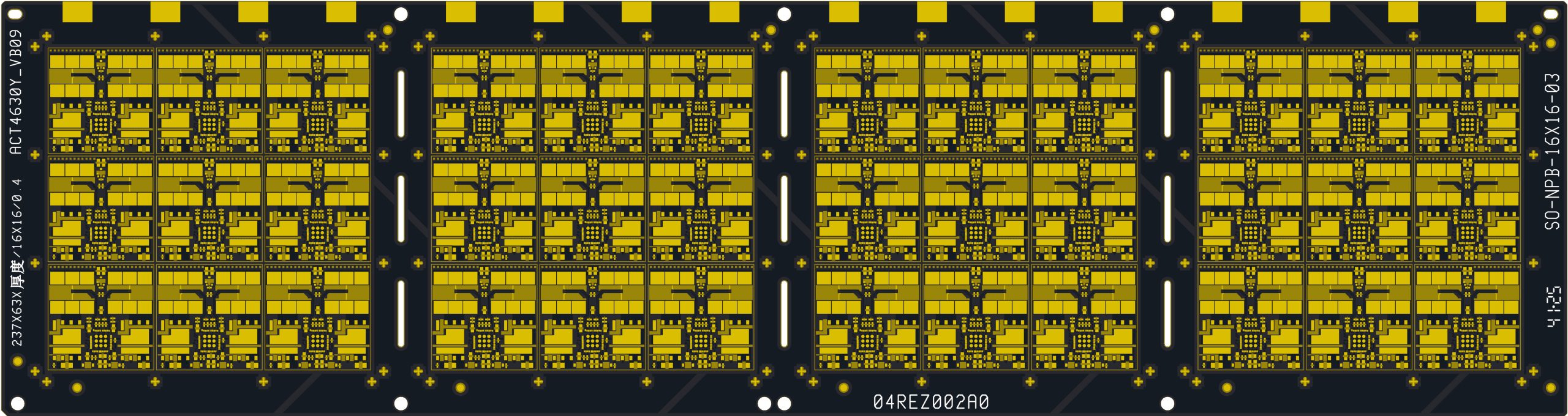

核心价值:通过垂直叠加,叠孔设计能够在单位面积内实现最大的互连密度。例如,10层HDI板采用叠孔设计后,布线密度可达到120线/cm²,是传统通孔设计的6倍以上。

1.2 错孔(Staggered Via):错位布局的智慧妥协

定义:错孔采用非对称设计,相邻层孔位在水平方向偏移1.5倍孔径距离(例如100μm孔径对应150μm偏移量)。这种设计方式旨在通过牺牲部分布线密度来换取更高的制造良率和更低的加工成本。

典型结构:

- 阶梯式盲孔:外层至不同内层,孔径梯度变化,以适应不同层间的互连需求。

- 交错埋孔:内层非对称连接,间距≥2倍孔径,以减少信号干扰和制造难度。

- 分层压合:允许分阶段完成不同层的压合,提高制造灵活性。

核心价值:错孔设计以牺牲10%-15%的布线密度为代价,换取制造良率提升至98%以上,同时降低30%以上的加工成本。这种设计方式在成本敏感的应用中更具吸引力。

二、制造工艺对比

2.1 叠孔的全流程技术攻坚

工艺流程:

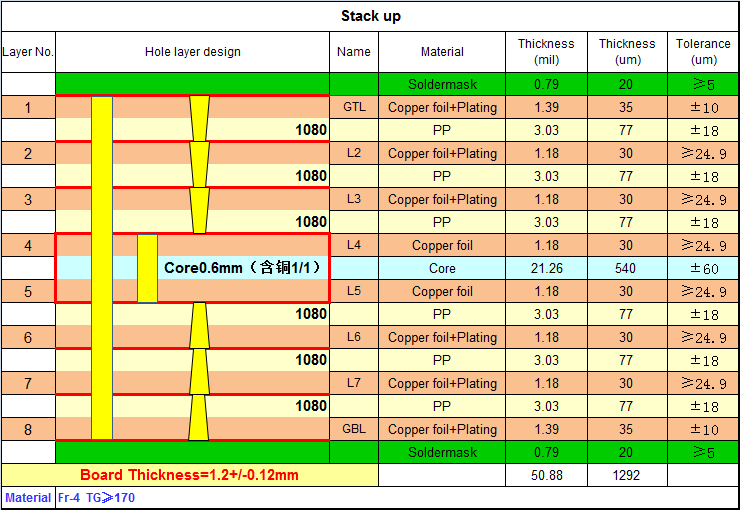

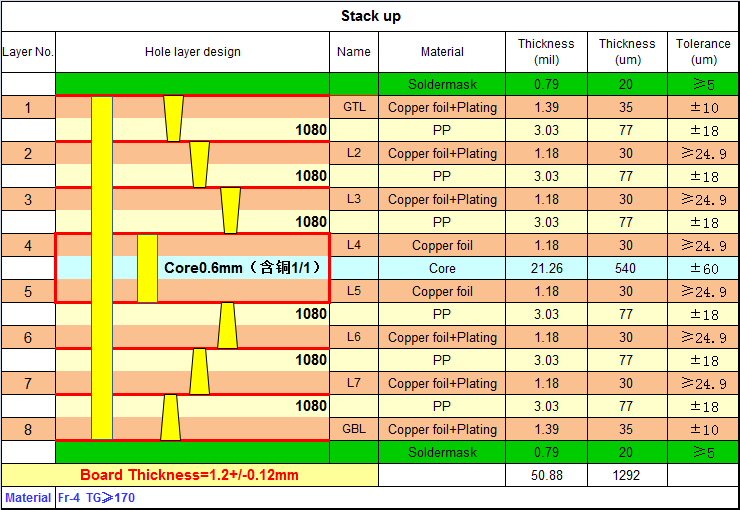

- 芯板预处理:采用Low-CTE基材(如M6型FR-4),表面粗化至Ra 3-5μm,以提高材料表面的附着力。

- 激光钻孔:外层采用CO₂激光(波长9.4μm)处理,内层则使用UV激光(355nm)穿透,实现高精度钻孔。

- 化学沉铜:采用钯催化体系沉积0.3μm种子层,溶液温度需稳定在28±0.5℃,以确保铜层的均匀性和附着力。

- 脉冲电镀:采用反向脉冲电源(频率1000Hz),实现10:1深宽比填孔,确保电镀层的致密性和导电性。

- 层压控制:每次压合需保持压力350psi±5%,升温速率≤3℃/min,以避免材料变形和层间剥离。

关键设备:

- 激光钻孔机(单台成本200万以上):用于实现高精度钻孔。

- X射线实时对位系统(精度±5μm):用于监测和控制各层孔位的对准精度。

- 真空填孔电镀线:采用真空环境进行电镀填孔处理,良率提升至95%以上。

2.2 错孔的柔性制造策略

工艺流程:

- 分步钻孔:外层采用激光孔(孔径80μm),内层则采用机械孔(孔径150μm),混合加工方式提高了制造灵活性。

- 选择性沉铜:调整各层沉积时间(外层15min/内层25min),实现差异化铜厚,以满足不同层间的导电需求。

- 交错压合:使用Z轴CTE<3ppm/℃的改性树脂,分3次完成8层3阶板压合,减少层间应力集中。

- 补偿设计:通过3D电磁仿真优化孔位偏移量,控制阻抗波动在±5%以内,确保信号完整性。

关键设备:

- 高精度机械钻床(定位误差±25μm):用于内层机械钻孔处理。

- 自动光学检测(AOI)系统:用于检测电路板上的缺陷和异常。

- 热循环测试箱(-55℃~150℃):用于评估电路板的热稳定性和可靠性。

三、技术难点深度剖析

3.1 叠孔的三大技术壁垒

壁垒一:纳米级对准控制

- 问题描述:材料热膨胀系数(CTE)差异导致各层偏移,影响孔位的对准精度。

- 解决方案:采用实时补偿算法修正±8μm偏差。例如,iPhone主板采用X射线对位系统,每平米增加200成本,以确保孔位的精确对准。

壁垒二:电镀填孔缺陷

- 问题描述:微孔深宽比超过1:1.2时,气泡残留率高达12%,影响电镀层的质量和导电性。

- 解决方案:引入真空填孔技术(设备投资增加400万),减少气泡残留。同时,100% X射线检测确保铜柱空洞率不超过5%,避免电阻上升。

壁垒三:层压应力集中

- 问题描述:垂直堆叠结构在温度循环中产生Z轴应力,导致微裂纹产生。

- 解决方案:使用CTE 4ppm/℃的ABF材料(Ajinomoto Build-up Film),减少层间应力集中。

3.2 错孔的四大挑战

挑战一:信号完整性管理

- 问题描述:非对称布局导致阻抗波动达±8%,影响信号传输质量。

- 解决方案:采用蛇形走线补偿技术(增加10%布线面积),通过3D场仿真优化回波损耗,降低至-25dB以下。

挑战二:机械钻孔精度

- 问题描述:0.15mm小孔钻头寿命仅5000孔,刀具成本占总加工费的18%;主轴转速需达30万RPM,定位精度要求高。

- 解决方案:采用高精度机械钻床和先进的刀具管理系统,提高钻孔精度和效率。

挑战三:散热路径优化

- 问题描述:错位结构使热传导路径延长20%,影响元件的散热效果。

- 解决方案:嵌入0.2mm厚铜块(成本增加500/m²),提高热传导效率。例如,特斯拉自动驾驶模块采用铜柱+石墨烯复合散热方案,确保元件在高温环境下的稳定运行。

挑战四:混合工艺兼容

- 问题描述:激光孔与机械孔的界面过渡区易出现15μm的铜层断裂,影响电路板的可靠性和导电性。

- 解决方案:开发过渡区加强电镀工艺(铜厚增加至35μm),提高铜层的附着力和导电性。

四、应用场景与成本博弈

4.1 叠孔的主战场

消费电子:

- 智能手机AP处理器(如苹果A16芯片,使用12层Any-layer叠孔):通过叠孔设计实现高集成度和高性能,满足智能手机对轻薄和高速处理的需求。

- 微型摄像头模组(0.35mm间距BGA出线):利用叠孔设计提高布线密度,确保摄像头模组的小型化和高像素输出。

高频通信:

- 5G毫米波天线(24GHz频段,叠孔损耗仅0.15dB/inch):叠孔设计减少信号损耗,提高天线传输效率。

- 卫星相控阵雷达(要求100%垂直对准精度):叠孔设计确保各层孔位的精确对准,满足雷达系统对高精度和高可靠性的需求。

成本结构:

- 8层3阶板制造成本3000元/m²,其中激光钻孔占450元/m²(主要源于微裂纹修复)。叠孔设计虽然提高了性能密度,但也带来了较高的制造成本。

4.2 错孔的优势领域

汽车电子:

- ECU控制模块(要求通过3000次温度循环测试):错孔设计通过优化散热路径和提高材料稳定性,确保ECU控制模块在高温环境下的稳定运行。

- 电池管理系统(6层2阶板成本控制在1800元/m²):错孔设计降低制造成本,提高加工良率,满足汽车电子对成本控制和可靠性的双重要求。

工业设备:

- 伺服驱动器(耐受200G机械振动):错孔设计通过优化结构布局和提高材料强度,确保伺服驱动器在恶劣环境下的稳定运行。

- 电力监控模块(15年使用寿命要求):错孔设计减少层间应力集中和信号干扰,提高电力监控模块的可靠性和使用寿命。

成本优势:

- 6层2阶板综合成本比叠孔低37%,其中机械钻孔占比达65%,检测成本仅为叠孔的1/3(允许10%孔位容差)。错孔设计在成本敏感的应用中更具竞争力。

五、未来技术演进方向

5.1 叠孔的技术突破

纳米孪晶铜技术:将电镀填孔电阻降低40%(英特尔已实现实验室验证),提高电路板的导电性能和能效。

原子层沉积(ALD):在孔径≤30μm时仍能保证5μm均匀铜层,提高电镀层的附着力和导电性。

光子集成对位:采用激光干涉仪将层间对准精度提升至±3μm,满足高端电子产品对高精度和高可靠性的需求。

5.2 错孔的创新路径

智能偏移算法:通过机器学习优化孔位布局,提升15%布线密度,满足高集成度电子产品的需求。

复合钻孔工艺:激光+等离子体混合钻孔技术将最小孔径缩小至50μm,提高钻孔精度和效率。

自适应压合材料:开发CTE梯度变化的半固化片材料,消除层间应力集中,提高电路板的可靠性和稳定性。

HDI叠孔和错孔的区别——技术选择的本质是价值平衡

HDI叠孔和错孔的区别本质上是性能密度与可靠经济的价值博弈。在智能手机等消费电子领域,叠孔仍是突破物理极限的必然选择;而在汽车、工业等场景中,错孔凭借优异的性价比持续扩大市场。随着材料科学与工艺设备的进步,两者的技术边界正在模糊——三星最新折叠屏手机主板已实现叠/错孔混合设计,这或许预示着下一代HDI技术的融合革命。在未来的发展中,叠孔与错孔技术将不断融合与创新,共同推动PCB行业向更高性能、更低成本、更可靠性的方向发展。

深泽多层电路是一家专业的PCB制造商,致力于高阶HDI、多层PCB、HDI打样、PCB打样、PCB快速打样、高频PCB、高速PCB、FPC、软硬结合板、SMT加工以及PCBA代工代料。他们提供一站式PCB及PCBA制造服务,不仅交期快速,而且价格具有竞争力。他们始终为客户提供高性价比和物美价廉的PCB及PCBA产品。

自2006年成立以来,一直致力于提供高阶HDI、多层PCB、HDI打样、PCB打样、PCB快速打样、高频PCB、高速PCB、FPC、软硬结合板、SMT加工以及PCBA代工代料等一站式制造服务。