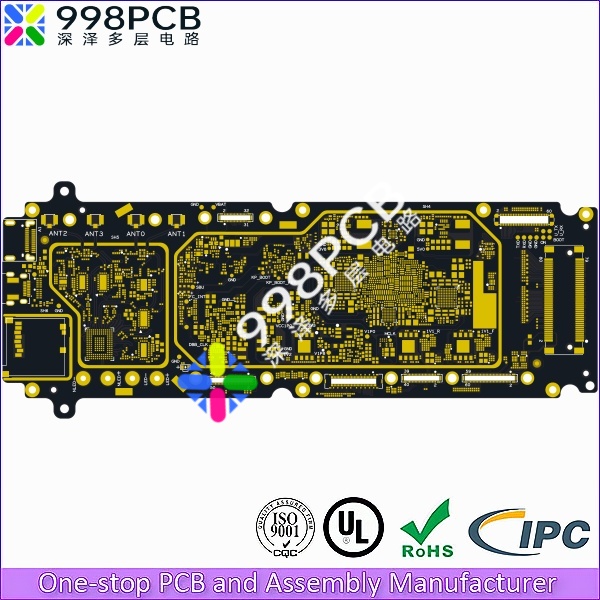

10层任意互联通信PCB

10层任意互联

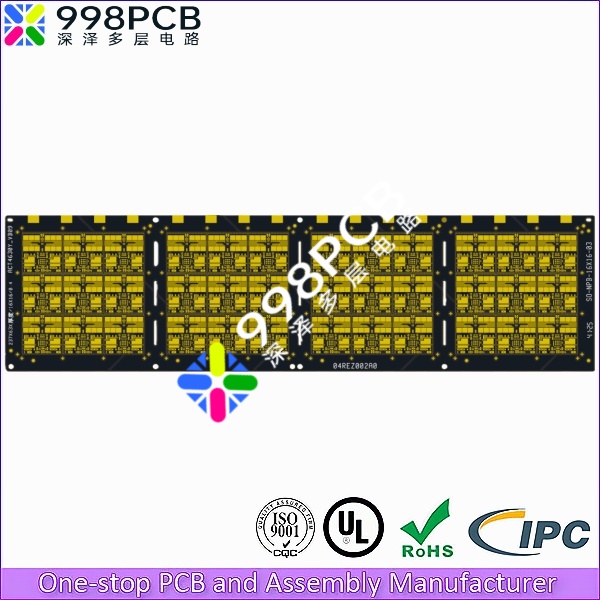

层数:10层任意互联

板材: FR4 EM-370(D) Tg170

板厚: 0.8mm

拼板尺寸: 145.3*58mm/1

外层铜厚: 1OZ

内层铜厚: HOZ

最小通孔: 0.20mm

最小盲孔: 0.076mm

线宽线距: 1.8/2mil

最小BGA: 0.2mm

特殊工艺:POFV

表面处理: OSP

10层任意层HDI核心板,过孔树脂塞孔,盲孔填孔电镀,主要5G通信、控制系统,智能辅助驾驶等,PCB难度高、要求严格,车规级要求。

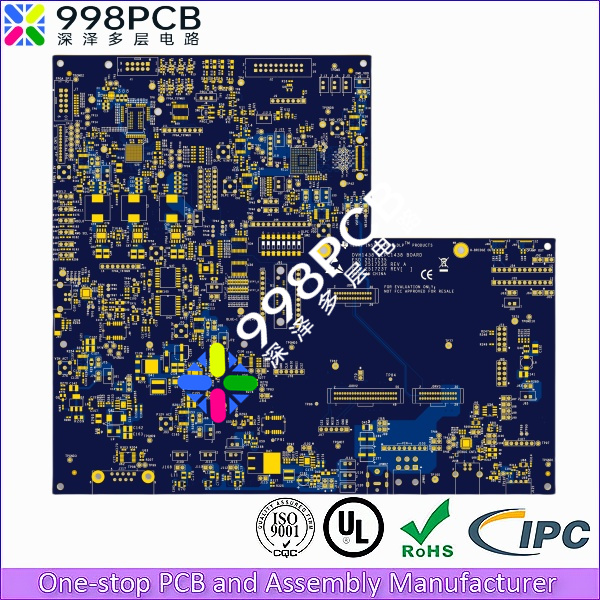

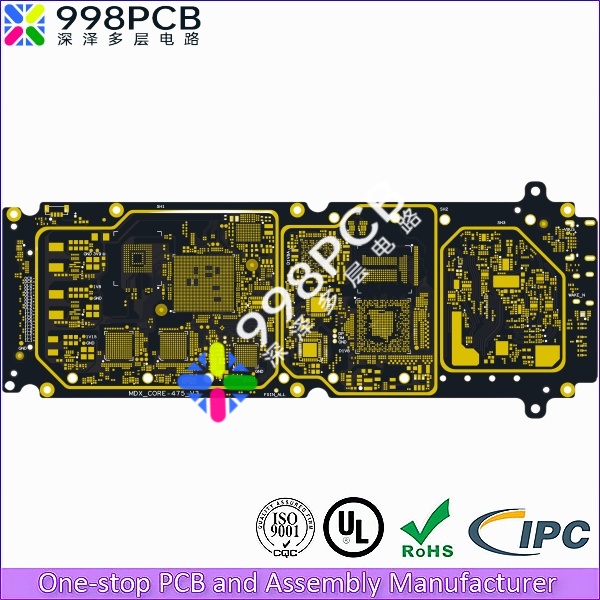

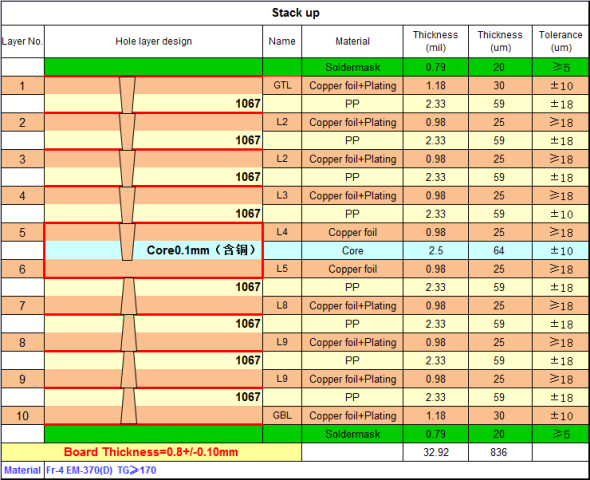

针对本产品10层任意层HDI板的特殊技术要求(内层最小线宽1.8mil、BGA焊盘0.2mm过孔需POFV工艺),我司在综合评估客户设计规范与制程边界条件后,制定了专项解决方案:鉴于内层铜厚过载导致蚀刻残留风险,采用0.076mm盲孔设计并优化填孔电镀工艺,通过1:1纵横比控制实现精密孔金属化;同时基于高速无卤板材特性及多层阻抗控制需求,特别设计如图示的阶梯式压合结构,通过介厚层精准配置(核心层采用超薄1080PP,外层搭配低损耗1067材料)和铜箔厚度梯度调整,在满足信号完整性要求的同时有效平衡工艺可行性。该方案已通过DFM仿真验证,可兼顾高频性能与生产良率。

10层任意互联通信PCB:技术演进与设计实践

在5G通信、数据中心和高速网络设备快速发展的推动下,高密度互连(HDI)PCB已成为支撑高频信号传输与复杂电路集成的核心载体。其中,10层任意层HDI通信PCB凭借其独特的多层堆叠架构与精细化工艺,成为实现高速率、低延时通信系统的关键技术。本文从技术难点、工艺创新、应用场景及未来趋势等维度,深度解析这一领域的核心技术与实践路径。

一、技术挑战与设计边界

1. 高密度互连的物理极限突破

10层任意层HDI的核心特征在于突破传统通孔(Through Via)的限制,采用盲埋孔(Blind/Buried Via)和激光微孔技术实现任意层间互连。其典型技术参数包括:

- 线宽/线距:内层最小线宽1.8mil(约45μm),间距2mil,需满足IPC-6012E Class 3标准;

- 过孔工艺:BGA区域0.2mm焊盘需采用POFV(Plated Over Filled Via)工艺,孔壁铜厚≥15μm以保障导电可靠性;

- 纵横比控制:盲孔直径0.076mm时,电镀填孔纵横比严格限制为1:1,避免孔内空洞率超过5%。

2. 信号完整性与材料适配

通信设备对信号损耗极为敏感,需同步解决以下问题:

- 介电常数稳定性:采用松下M7NE或Isola FR408HR等高速无卤板材,Dk值波动控制在±0.05(1GHz下);

- 阻抗匹配:差分对阻抗公差±7%,需通过叠层仿真优化(如Polar SI9000工具),核心层使用超薄1080PP(厚度0.075mm)降低串扰;

- 散热设计:通过铜箔厚度梯度调整(外层2oz、内层1oz)平衡导电性与热扩散效率。

二、工艺创新与制造实践

1. 阶梯式压合结构设计

针对10层任意层HDI的复杂性,典型叠层方案采用“4+2+4”对称结构:

- 内层核心:2层超低损耗材料(如Nelco N7000-13SI)构成信号传输主干,介厚0.13mm;

- 次外层:搭配高TG环氧树脂(Tg≥170℃)提升机械强度;

- 外层处理:化学沉银+OSP双工艺,兼顾高频性能与焊接可靠性。

2. 关键制程突破

- 精密图形转移:采用LDI(激光直接成像)技术,实现1.8mil线宽±0.2mil精度,减少侧蚀问题;

- 填孔电镀优化:脉冲电镀工艺搭配有机添加剂,盲孔填铜率提升至98%以上,表面平整度Ra<1.5μm;

- 层压控制:真空热压机分段加压(0.8MPa→1.5MPa→2.0MPa),确保层间结合力>1.2N/mm。

3. 全流程质量验证

- DFM仿真验证:利用Valor NPI软件进行热应力分析,预测板翘曲度<0.5%;

- AOI/X-ray检测:BGA区域100% X射线扫描,焊球直径公差±0.02mm;

- 可靠性测试:85℃/85%RH环境老化1000小时,阻抗变化率<3%。

三、典型应用场景与案例分析

1. 5G基站AAU板卡

某头部设备商的32T32R Massive MIMO天线板案例:

- 设计要求:10层PCB集成2048个射频通道,支持28GHz毫米波传输;

- 解决方案:采用任意层盲孔+局部背钻技术,通道间隔离度提升至-65dB;

- 成效:整板尺寸缩减40%,功耗降低15%,已批量应用于全球5G基站。

2. 数据中心光模块

400G QSFP-DD光引擎PCB实例:

- 挑战:56Gbps PAM4信号需满足插损<0.5dB/inch(16GHz);

- 技术路径:

- 使用Megtron 6材料降低介质损耗(Df=0.002@10GHz);

- 铜箔表面粗化处理(RTF铜),粗糙度Rz≤2μm;

- 成果:误码率(BER)<1E-15,通过OIF-CEI-56G-VSR-PAM4认证。

四、未来技术演进方向

1. 材料体系升级

- 超低损耗基材:罗杰斯RO4835LoPro、台光EM-888K等材料Df值向0.0015突破;

- 嵌入式元件:在PCB内层集成电阻/电容(如AVX Thin Film技术),减少表贴器件数量。

2. 工艺极限拓展

- 半加成法(mSAP):实现1mil线宽/间距,支撑112Gbps高速接口;

- 3D堆叠互连:通过硅转接板(Interposer)实现多芯片异构集成。

3. 智能化制造转型

- AI缺陷预测:利用深度学习分析AOI图像,缺陷识别准确率>99%;

- 数字孪生平台:ANSYS Twin Builder构建虚拟产线,良率预判误差<0.5%。

五、结语

10层任意层HDI通信PCB的设计与制造,是材料科学、工艺工程与系统集成的深度融合。随着5G-A与6G技术的演进,行业需在超精细线路加工、多物理场协同仿真及绿色制造等领域持续突破。未来,这一技术将不仅是通信设备的“骨骼”,更将成为智能时代信息传输的“神经网络”。